LABORATORIO: Por medio de dos circuito Aestables con 555, deseamos en un LED RGB, lograr la intermitencia del Led Rojo, Led Verde y Led Azul incorporados en el led RGB, tanto de una forma lenta como rápidamente.Debe haber un mensaje asociado a cada situación. Por medio de un Dip-Switch de 3 interruptores se debe seleccionar la operación así:

S2 S1 S0

0 0 0 Led Rojo Lento

0 0 1 Led Verde Lento

0 1 0 Led Azul Lento

0 1 1 Leds apagados

1 0 0 Led Rojo Rápido

1 0 1 Led Verde Rápido

1 1 0 Led Azul Rápido

1 1 1 Leds apagados

Se pretende con este trabajo de laboratorio manejar los conceptos de Multiplexaje y Demultiplexaje, y adquirir destreza en la aplicación del sintetizador de sonido ISD1964.

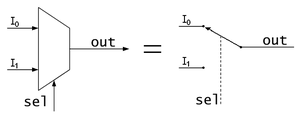

MULTIPLEXORES:

Los multiplexores son circuitos digitales combinatorios

con varias entradas y una única salida, dotados de entradas de control capaces de seleccionar una, y sólo una, de las entradas de datos para permitir su transmisión desde la entrada seleccionada hacia dicha salida.

Estos circuitos combinacionales poseen  líneas de entrada de datos, una línea de salida y n entradas de selección. Las entradas de selección indican cuál de estas líneas de entrada de datos es la que proporciona el valor a la línea de salida.

líneas de entrada de datos, una línea de salida y n entradas de selección. Las entradas de selección indican cuál de estas líneas de entrada de datos es la que proporciona el valor a la línea de salida.

Por ejemplo, la gráfica anterior presenta un Multiplexor o MUX de 2 entradas y 1 Salida, el cual dispone de una entrada de selección o de control. Es equivalente a un conmutador controlado: Si la entrada de selección sel es 0, la salida out es igual a la entrada de dato I0, y si la entrada de selección sel = 1, out se hace igual a I1.

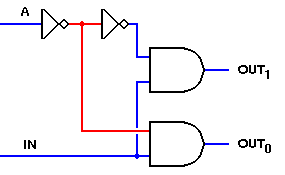

Un Multiplexor de 2 a 1 se implementa con 1 compuerta OR, 2 compuertas AND y 1 inversor tal como se muestra a continuación:

Si S = 0,la salida de la primera AND es I0, y la de la segunda AND es 0,por consiguienteY = I0 + 0 = I0.

Si S=1,la salida de la primera AND es 0, y la de la segunda AND es I1,por consiguiente Y = 0 + I1 = I1.

Luego si I0 es la salida 3 del 555 que genera ondas de baja frecuencia y si en Y colocamos un LED con cátodo a tierra, al hacer la entrada de selección S = 0, el led debe parpadear lentamente. Si en la entrada I1 está dispuesta la salida 3 de otro circuito astable de mas frecuencia que el anterior, al seleccionar S =1, el led debe producir la intermitencia ahora de forma mucho más rápida que la anterior.

Luego es claro que para seleccionar el Astable Lento o Rápido, requerimos de un MUX de 2 entradas/1 salida.

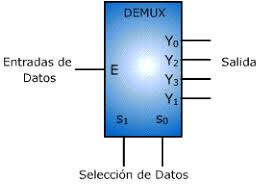

DEMULTIPLEXORES:

Un

Demultiplexor o un DEMUX actúa en forma inversa a como lo hace un

Multiplexor.

Tal como se observa en la siguiente figura, para un MUX de 1 entrada/2 salidas, si la entrada de selección es

sel = 0, O0 = in, pero si

sel = 1, O1 = in. La única entrada

in pasa a la salida O0 ó la salida O1 según se seleccione

sel con

0 ó

1.

Un MUX de 1 entrada/ 2 salidas se puede implementar como se muestra a continuación, donde A es la entrada de selección y IN es la entrada de dato.

Si A = 0, OUT 0 = IN, pero si A = 1, entonces OUT 1 = IN.

El lector debe haberse dado cuenta que el circuito lógico es exáctamente igual al de un decodificador de 1 entrada de dato, con entrada de habilitación o Enable activo en nivel alto y 2 salidas activas en nivel alto.

En el decodificador IN era la entrada de habilitación (ENABLE).

La conclusión que se obtiene es que un DECODIFICADOR con ENABLE se puede utilizar como DEMULTIPLEXOR.

El

Enable en el decodificador, además de permitir la expansión del decodificador para implementar con 2 de ellos uno del doble de capacidad, es esencial para que el decodificador pueda trabajar también como

demultiplexor.

En electrónica digital, en general, se puede definir un demultiplexor como un circuito combinacional que tiene una entrada de información de datos d y n entradas de control que sirven para seleccionar una de las 2n salidas, por la que ha de salir el dato que presente en la entrada. Esto se consigue aplicando a las entradas de control la combinación binaria correspondiente a la salida que se desea seleccionar. Por ejemplo,en la gráfica siguiente vemos un DEMUX de 1 entrada de datos, y 4 salidas, el cual requiere de 2 entradas de selección de datos.

Si queremos que la información que tenemos en la entrada de datos, salga por la salida Y0, en la entrada de control se ha de seleccionar, S1 = 0, S0 = 0, debido a que 00 es el 0 en binario. Con S1 = 0, S0 = 1, la Entrada de Datos sale por Y1; con S1= 1, S0 = 0, Y2 se conecta con la entrada de Datos, y si S1 S0 es 11, La Entrada de Datos que puede ser por ejemplo un tren de pulsos generado por un circuito de reloj como el 555 se conecta con la salida Y3, debido a que 11 es el 3 en Binario.

Un DEMUX de 1 entrada /4 salida se puede implementar con un DECODER de 2 entradas/4 salidas, provisto de entrada de habilitación.

Veamos la tabla de verdad de un decodificador con Enable y Salidas activas en nivel bajo.

Entradas Salidas

G B A Y0 Y1 Y2 Y3

0 0 0 0 1 1 1

0 0 1 1 0 1 1

0 1 0 1 1 0 1

0 1 1 1 1 1 0

1 X X 1 1 1 1

Si cambiamos G por IN , B por S1 y A por S0, la tabla nos quedará asÍ:

Entradas Salida

IN S1 S0 Y0 Y1 Y2 Y3

0 0 0

0 1 1 1

0 0 1 1

0 1 1

0 1 0 1 1

0 1

0 1 1 1 1 1

0

1 X X 1 1 1 1

Podemos concluir que si S1 S0 = 00, Y0 = 0, que es el nivel lógico de IN, pero si S1 S0 = 00, siendo IN =1, también Y0 = 1. Luego si S1S0 = 00, se tiene que Y0 = IN. Así mismo si S1S0 = 01, Y1 = IN, si S1S0 = 10, Y2 = IN, y finalmente, si S1S0 =11, entonces la salida Y3 = IN.

Podemos resumir en la siguiente tabla resumida:

S1 S0 = 00 entonces Y0 = IN

S1 S0 = 01 entonces Y1 = IN

S1 S0 = 10 entonces Y2 = IN

S1 S0 = 11 entonces Y3 = IN

Con estas ideas del

demultiplexor podemos volver al laboratorio, y vemos el esquema completo con el

multiplexor:

El Led RGB trae 3 leds incorporados: RED, GREEN,BLUE, tal como se muestra.

Puede ser de Cátodo o de Anodo común.

Respecto al sintetizador de sonido ISD1964 se direcciona con S2 S1 S0, puenteando con A2 A1 A0 respectivamente. A3 = 0 ( tierra) por cuanto se trabajan solo los 3 bits menos significativos.

A2 A1 A0 Mensajes a grabar y reproducir:

0 0 0 Led Rojo Lento

0 0 1 Led Verde Lento

0 1 0 Led Azul Lento

0 1 1 Leds apagados

1 0 0 Led Rojo Rápido

1 0 1 Led Verde Rápido

1 1 0 Led Azul Rápido

1 1 1 Leds apagados

Para los mensajes con el sintetizador de sonido debe disponer de un protoboard con la plaqueta con dip-switch y los pulsadores para grabar y reproducir. Recuerde que hay 2 formas de reproducir el mensaje grabado: por flanco de bajada o por nivel.

Para implementar el MUX 2 a 1 y el DEMUX 2 a 1 se puede utilizar una sóla GAL22V10, trabajando los esquemáticos o tablas de verdad.

Si no se dispone del programador de la GAl, habría que usar lo que el comercio ofrece en TTL o en CMOS, y en lugar de programar habría que cablear más.

El chip 74157 dispone de 4 Multiplexores de 2 entradas/1 salida.

El integrado dispone de un único selector (pin 1); además, para poderlo expandir, trae una entrada de habilitación Strobe (pin 15).

El diagrama lógico del 74157 se muestra a continuación:

El integrado 74LS139 dispone de 2 DEMUX de 1 entrada/4 salidas.

Observe que las salidas del DEMUX son activas en nivel bajo. Los Leds del RGB deben ser de ánodo común.

Si se dispone del Decodificador/Demultiplexor 74154 también se puede utilizar como DEMUX de 1 entrada/4 salidas que es lo que se requiere en este laboratorio. Las entradas de selección D y C se llevan a tierra, y sólo se trabaja con B y A. La entrada del DEMUX es un enable, el G1 estando G2 tambien a tierra. Como G1 es activo en nivel bajo, niega la entrada. Sólo se utilizan las salidas del "0", del "1" y del "2" del decodificador. Las demás no se conectan porque no se necesitan. Con la salida "0" se maneja el Led Rojo, con "1" el led verde y con la "2" el led azul del led tricolor RGB.

Si tenemos D C B A = 0 0 0 0, por ejemplo, entonces la entrada por G1 se invierte y sale por "0" también negada.Luego si entra un CERO por "0" sale tambien un CERO y si entra un UNO sale un UNO lógico. Si el Led tiene su ánodo a Vcc se enciende con el CERO y se apaga con el UNO. Como las otras salidas "1" y "2" permanecen en UNOS no se deben encender los Leds verde y azul, sino sólamente el LED rojo a la salida "0", pero siempre y cuando los Leds sean de configuración Anodo Común.

Dejamos al lector con esta animación que encontramos en Wikipedia, la cual ilustra muy bien los conceptos de Multiplexaje y Demultiplexaje que hemos estado estudiando:

Para el caso mostrado, el MUX conmuta 5 entradas a 1 salida; el DEMUX hace lo contrario, la entrada la conmuta a 5 salidas.

.JPG)

.JPG)

.JPG)